依然水深が深いOEM市場は、最近特に問題を抱えています。Samsung が 2027 年に 1.4nm を大量生産し、TSMC が半導体の王座に戻る可能性があると述べた後、Intel は IDM2.0 を強力に支援する「システムレベルの OEM」も立ち上げました。

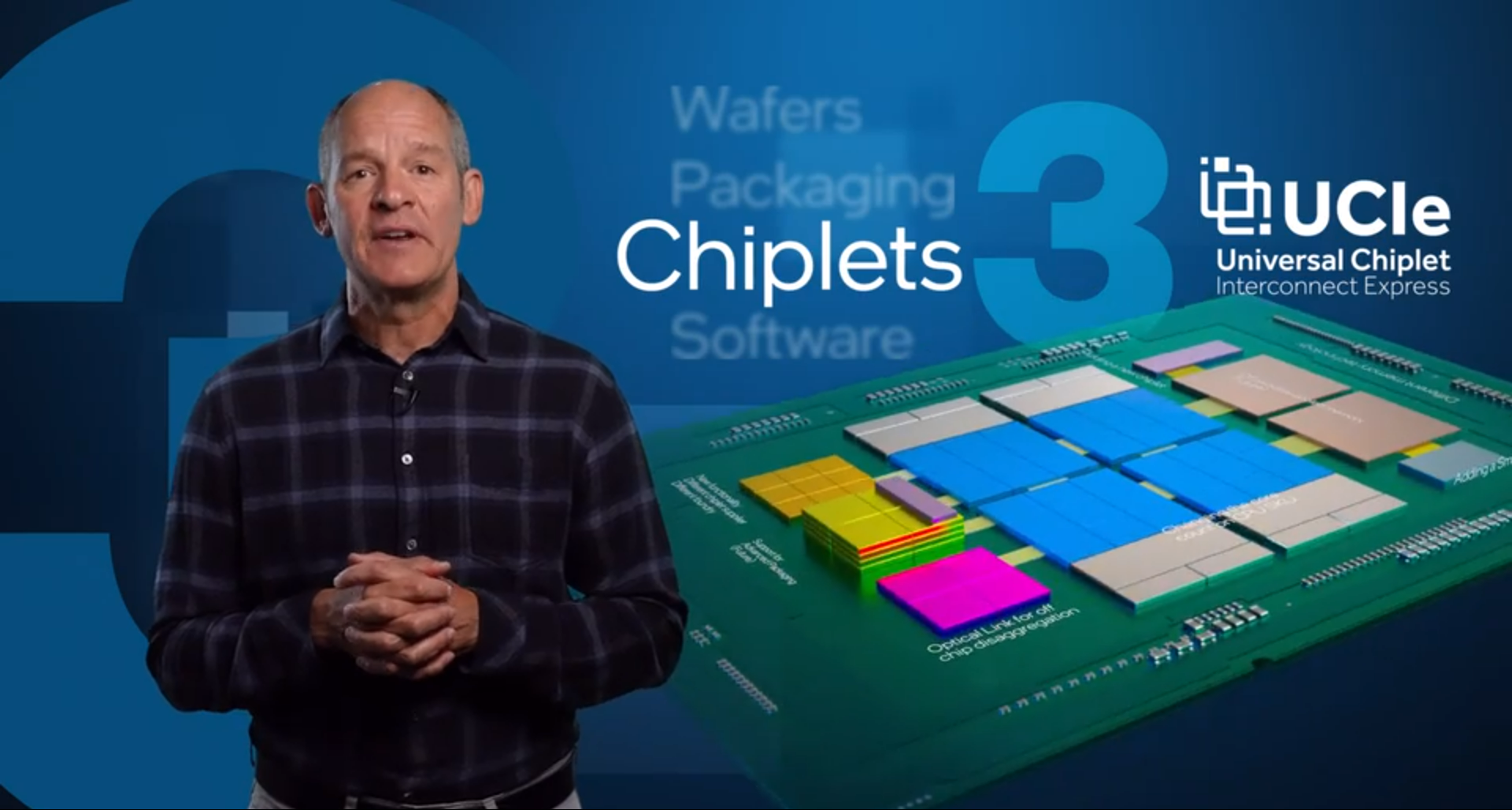

最近開催された Intel On Technology Innovation Summit で、CEO の Pat Kissinger は、Intel OEM Service (IFS) が「システム レベル OEM」の時代を迎えると発表しました。ウェーハ製造機能のみを顧客に提供する従来の OEM モードとは異なり、インテルはウェーハ、パッケージ、ソフトウェア、およびチップをカバーする包括的なソリューションを提供します。キッシンジャー氏は、「これは、システム オン チップからシステム イン パッケージへのパラダイム シフトを示している」と強調しました。

Intel は IDM2.0 に向けた動きを加速させた後、最近、一定の行動をとっています。x86 のオープン、RISC-V 陣営への参加、タワーの買収、UCIe アライアンスの拡大、数百億ドル規模の OEM 生産ライン拡張計画の発表などです。これは、OEM 市場で大きな展望を持つことを示しています。

さて、システムレベルの受託製造に「大きな動き」を示したインテルは、「三皇」の戦いにさらにチップを追加するのでしょうか?

システムレベルの OEM コンセプトの「出世」はすでにトレースされています。

ムーアの法則の減速後、トランジスタ密度、消費電力、およびサイズのバランスを達成することは、より多くの課題に直面しています。しかし、新しいアプリケーションは、高性能で強力なコンピューティング能力と異種統合チップをますます要求しており、業界は新しいソリューションを探求するようになっています。

設計、製造、高度なパッケージング、そして最近のチップレットの台頭により、ムーアの法則の「存続」とチップ性能の継続的な変化を実現することがコンセンサスになったようです。特に将来の限定的なプロセス縮小の場合、チップレットと高度なパッケージングの組み合わせは、ムーアの法則を打ち破るソリューションになるでしょう。

接続設計、製造、高度なパッケージングの「主力」である代替工場には、明らかに固有の利点と活性化できるリソースがあります。この傾向を意識して、TSMC、Samsung、Intel などのトッププレイヤーはレイアウトに力を入れています。

半導体OEM業界の上級者の意見では、システムレベルのOEMは今後の必然的な傾向であり、これはパンIDMモードの拡張に相当し、CIDMと同様ですが、違いはCIDMが一般的なタスクであるということです。さまざまな企業を接続する一方で、汎 IDM はさまざまなタスクを統合して、顧客にターンキー ソリューションを提供します。

Intel は Micronet とのインタビューで、システム レベル OEM の 4 つのサポート システムから、Intel には有利な技術の蓄積があると述べました。

ウェーハ製造レベルでは、Intel は、RibbonFET トランジスタ アーキテクチャや PowerVia 電源などの革新的なテクノロジを開発し、4 年以内に 5 つのプロセス ノードを促進する計画を着実に実行しています。インテルは、EMIB や Foveros などの高度なパッケージング テクノロジも提供して、チップ設計企業がさまざまなコンピューティング エンジンとプロセス テクノロジを統合できるようにします。コアのモジュラー コンポーネントは、設計の柔軟性を高め、業界全体を価格、性能、消費電力の革新に駆り立てます。インテルは、さまざまなサプライヤーやさまざまなプロセスのコアがより適切に連携できるように、UCIe アライアンスの構築に取り組んでいます。ソフトウェアに関しては、Intel のオープンソース ソフトウェア ツールである OpenVINO と oneAPI により、製品の提供が加速され、顧客は生産前にソリューションをテストできるようになります。

システム レベル OEM の 4 つの「プロテクター」により、Intel は、1 つのチップに統合されるトランジスタが現在の 1000 億から 1 兆レベルに大幅に拡大すると予想していますが、これは基本的に当然の結論です。

「インテルのシステム レベル OEM の目標は、IDM2.0 の戦略に準拠しており、インテルの将来の発展の基盤となる大きな可能性を秘めていることがわかります。」上記の人々は、インテルに対する楽観的な見方をさらに表明しました。

「ワンストップ チップ ソリューション」で有名なレノボと、今日の「ワンストップ製造」システム レベル OEM の新しいパラダイムは、OEM 市場に新たな変化をもたらす可能性があります。

勝利のチップ

実際、Intel はシステム レベルの OEM 向けに多くの準備を行ってきました。上記のさまざまなイノベーション ボーナスに加えて、システム レベルのカプセル化の新しいパラダイムに向けた取り組みと統合の取り組みも見られるはずです。

半導体業界のChen Qi氏は、既存のリソースの確保から、Intelは完全なx86アーキテクチャIPを持っており、これが本質であると分析しました。同時に、Intel には PCIe や UCle などの高速 SerDes クラス インターフェイス IP があり、チップレットを Intel コア CPU とより適切に組み合わせて直接接続するために使用できます。また、インテルはPCIeテクノロジー・アライアンスの規格策定を統括しており、PCIeをベースに開発されたCXLアライアンスやUCle規格もインテルが主導しており、インテルがコアIPと非常に重要なハイレベルの両方をマスターしていることに相当します。 -SerDes テクノロジーと規格の高速化。

「インテルのハイブリッド パッケージング技術と高度なプロセス能力は弱くありません。x86IP コアおよび UCIe と組み合わせることができれば、システム レベルの OEM 時代に、より多くのリソースと発言力を持ち、強力なままであり続ける新しいインテルを生み出すことができます。」Chen Qi は Jiwei.com に語った。

これらはすべてインテルのスキルであり、これまで簡単には発揮されないことを知っておく必要があります。

「過去に CPU 分野で確固たる地位を築いていたため、Intel はシステムの重要なリソースであるメモリ リソースをしっかりと管理していました。システム内の他のチップがメモリ リソースを使用する場合は、CPU を介してそれらを取得する必要があります。したがって、インテルはこの動きを通じて他社のチップを制限することができます。過去には、業界はこの「間接的な」独占について不満を述べていました。」Chen Qi 氏は次のように説明しています。ケーキをテーブルに置く。」

業界の観点から見ると、IC 設計と高度なパッケージングにおけるインテルのテクノロジーとレイアウトは依然として非常に堅実です。Isaiah Research は、Intel のシステム レベル OEM モードへの移行は、これら 2 つの側面の利点とリソースを統合し、設計からパッケージングまでのワンストップ プロセスの概念を通じて他のウェーハ ファウンドリーを差別化することであり、より多くの注文を獲得するためであると考えています。将来の OEM 市場。

「このように、ターンキー ソリューションは、一次開発と R&D リソースが不十分な小規模企業にとって非常に魅力的です。」Isaiah Research は、Intel の動きが中小規模の顧客を引き付けることについても楽観的です。

一部の業界専門家は、率直に言って、Intel システム レベルの OEM の最も現実的な利点は、Google、Amazon などの一部のデータ センターの顧客との Win-Win の協力関係を拡大できることです。

「まず、Intel は自社の HPC チップで Intel X86 アーキテクチャの CPU IP を使用することを許可することができます。これは、CPU 分野で Intel の市場シェアを維持するのに役立ちます。第 2 に、インテルは UCle などの高速インターフェイス プロトコル IP を提供できます。これは、顧客が他の機能 IP を統合するのにより便利です。第三に、インテルはストリーミングとパッケージングの問題を解決するための完全なプラットフォームを提供し、インテルが最終的に参加する Amazon バージョンのチップレット ソリューション チップを形成します。より完璧なビジネス プランになるはずです。」 上記の専門家はさらに補足します。

まだまだ補習が必要です

ただし、OEM はプラットフォーム開発ツールのパッケージを提供し、「顧客第一」のサービス コンセプトを確立する必要があります。インテルの過去の歴史から、OEM も試みましたが、結果は満足のいくものではありませんでした。システム レベルの OEM は、IDM2.0 の目標を実現するのに役立ちますが、隠れた課題を克服する必要があります。

「ローマが一日にして成らずのように、OEM とパッケージングは、技術が強力であればすべてが OK であるとは限りません。インテルにとって最大の課題は依然として OEM 文化です。」Chen Qi は Jiwei.com に語った。

Chen Qijin 氏はさらに、製造やソフトウェアなどのエコロジカルな Intel も、お金を使ったり、技術移転やオープン プラットフォーム モードで解決できる場合、Intel の最大の課題は、システムから OEM 文化を構築し、顧客とのコミュニケーションを学ぶことであると指摘しました。 、顧客に必要なサービスを提供し、差別化されたOEMのニーズを満たします。

Isaiah 氏の研究によると、Intel が補完する必要があるのは、ウェーハ ファウンドリの能力だけです。継続的かつ安定した主要顧客と各プロセスの歩留まり向上に役立つ製品を持つ TSMC と比較して、Intel はほとんどが自社製品を生産しています。製品カテゴリと容量が限られている場合、インテルのチップ製造の最適化能力は限られています。システムレベルの OEM モードを通じて、Intel はデザイン、高度なパッケージング、コアグレインなどのテクノロジーを通じて一部の顧客を引き付け、少数の多様な製品から段階的にウエハー製造能力を向上させる機会を得ています。

さらに、システム レベル OEM の「トラフィック パスワード」として、Advanced Packaging と Chiplet も独自の困難に直面しています。

システムレベルのパッケージングを例にとると、その意味からすれば、ウェーハ生産後に異なるDieを統合することと同じですが、簡単ではありません。TSMC を例にとると、Apple 向けの初期のソリューションから AMD 向けの後の OEM まで、TSMC は高度なパッケージング技術に長年を費やし、CoWoS、SoIC などのいくつかのプラットフォームを立ち上げましたが、最終的にそれらのほとんどはこれは、顧客に「積み木のようなチップ」を提供すると噂されている効率的なパッケージング ソリューションではありません。

最後に、TSMC はさまざまなパッケージング技術を統合した後、3D Fabric OEM プラットフォームを立ち上げました。同時に、TSMC は、UCle Alliance の形成に参加する機会をつかみ、独自の標準を UCIe 標準と結び付けようとしました。これにより、将来の「ビルディング ブロック」の促進が期待されます。

コア粒子結合の鍵は、「言語」の統一、つまりチップレットインターフェースの標準化にあります。このため、Intel は再び影響力を行使して、PCIe 規格に基づくチップ間相互接続の UCIE 規格を確立しました。

明らかに、標準の「通関手続き」にはまだ時間が必要です。The Linley Group の社長兼チーフ アナリストである Linley Gwennap は、Micronet とのインタビューで、業界が本当に必要としているのはコアを接続する標準的な方法であるが、企業は新たな標準を満たす新しいコアを設計する時間が必要であると述べました。ある程度の進歩はありますが、まだ2〜3年かかります。

半導体の先輩は、多面的な視点から疑問を表明しました。Intelが2019年にOEMサービスから撤退し、3年以内に復帰した後、Intelが再び市場に受け入れられるかどうかを観察するには時間がかかります.技術面では、インテルが2023年に投入すると予想される次世代CPUは、プロセス、ストレージ容量、I/O機能などの面でまだ優位性を発揮しにくい。また、インテルのプロセス設計図は数回遅れているしかし、現在は組織再編、技術向上、市場競争、工場建設などの困難な課題を同時に遂行しなければならず、これまでの技術的課題よりも未知のリスクが追加されているようです。特に、Intel が新しいシステム レベルの OEM サプライ チェーンを短期的に確立できるかどうかも大きな試練です。

投稿時間: 2022 年 10 月 25 日